- 您现在的位置:买卖IC网 > Sheet目录1996 > HMC703LP4E (Hittite Microwave Corporation)IC FRACT-N PLL W/SWEEPR 24QFN

P

LL

s

-

s

M

T

6 - 45

HMC703LP4E

v02.0813

8 GHz fractional syntHesizer

For price, delivery and to place orders: Hittite Microwave Corporation, 2 Elizabeth Drive, Chelmsford, MA 01824

978-250-3343 978-250-3373 fax Order On-line at www.hittite.com

Application Support: pll@hittite.com

reGister MaP

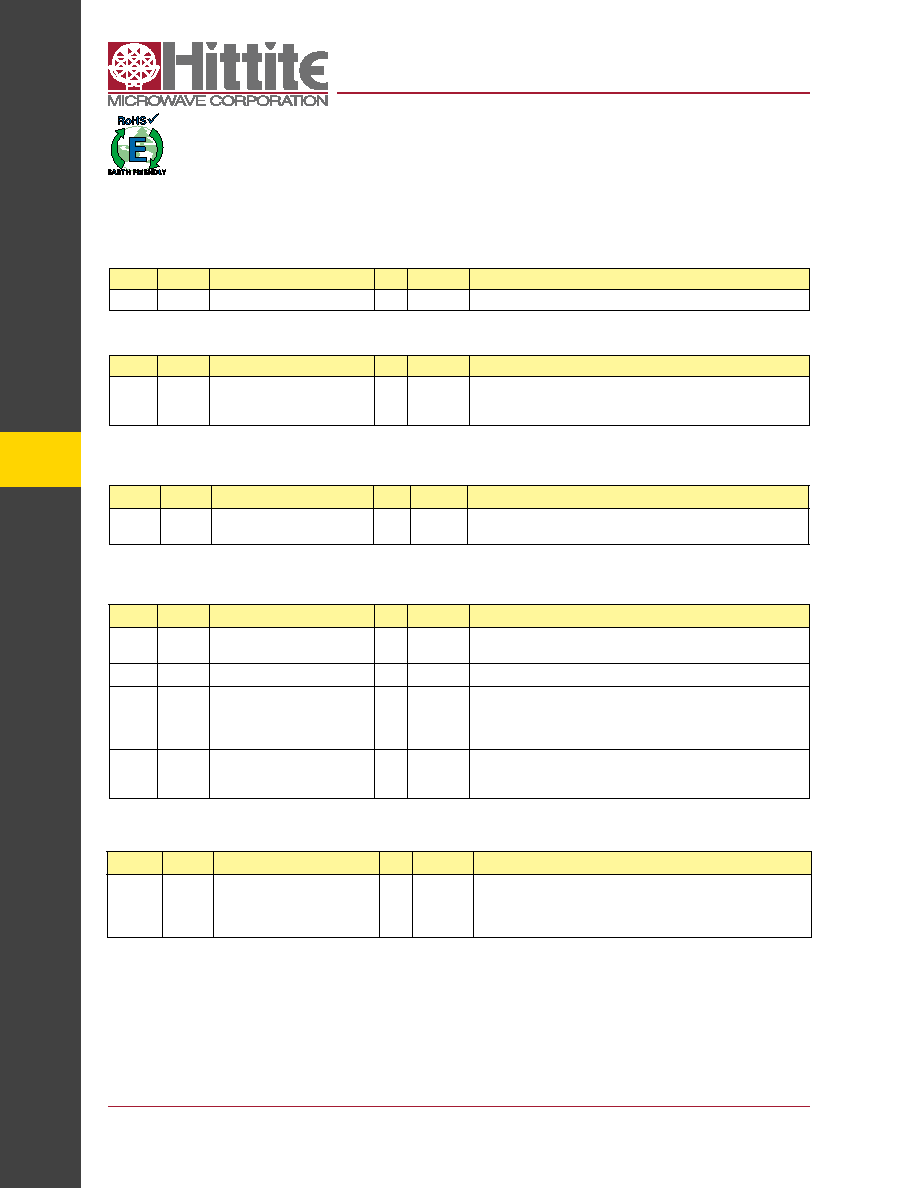

table 13. reg 00h iD register (read only)

BIT

TYPE

NAME

W

DEFLT

DEsCRIPTION

[23:0]

RO

chip_ID

24

97370h

PLL ID

table 13. reg 00h open Mode read address/rst strobe register (Write only) (Continued)

BIT

TYPE

NAME

W

DEFLT

DEsCRIPTION

[4:0]

WO

ReadAddr

5

0

Write the intended read address to this register for Open Mode

register reads. On the 1st sPI clock of the next cycle the data is

read and the shift-out begins.

table 13. reg 00h open Mode read address register (Write only) (Continued)

BIT

TYPE

NAME

W

DEFLT

DEsCRIPTION

5

WO

softRst

1

0

soft-reset. When 1, it Resets the registers to POR state, and is-

sues POR to analog.

table 14. reg 01h rst register

BIT

TYPE

NAME

W

DEFLT

DEsCRIPTION

0

R/W

EnPinsel

0

If 1, the master chip enable is taken from the pin rather than from

the sPI.

1

R/W

EnFromsPI

1

The master Enable from the sPI. Write a 0 to power-down the chip.

[9:2]

R/W

EnKeepOns

8

0

While the chip is disabled, the user has the option to keep the

following sub-circuits active by writing a 1 to the appropriate bits.

[2] Bias, [3] PFD, [4] CHP, [5] RefBuf, [6] VCOBuf, [7] GPO, [8]

VCODIVA, [9] VCODIVB

10

R/W

EnsyncChpDis

1

0

If 1, then following a disable event, the charge-pump is disabled

synchronously on the falling edge of the divided reference to tri-

state the charge pump without transient.

table 15. reg 02h refDiV register

BIT

TYPE

NAME

W

DEFLT

DEsCRIPTION

[13:0]

R/W

rdiv

14

1

Reference Divider ’R’ Value

Divider use also requires refBufEn Reg08[3]=1

min 1d

max 16383d

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

HMC704LP4E

IC FRACT-N PLL 16BIT 24QFN

HMC830LP6GE

IC FRACT-N PLL W/VCO 40QFN

HMP8117CNZ

IC VIDEO DECODER NTSC/PAL 80PQFP

HMP8156ACNZ

IC VIDEO ENCODER NTSC/PAL 64MQFP

HSP45102SC-40Z

IC OSC NCO 40MHZ 28-SOIC

HSP45106JC-33Z

IC OSC NCO 33MHZ 84-PLCC

HSP45116AVC-52Z

IC OSC NCO 52MHZ 160-MQFP

ICL7109EPL+

IC ADC 12BIT 3-ST 40-DIP

相关代理商/技术参数

HMC703LP4ETR

制造商:Hittite Microwave Corp 功能描述:IC FRACT-N PLL W/SWEEPR 24QFN 制造商:Hittite Microwave Corp 功能描述:8 GHz Fractional-N PLL with Sweeper

HMC7043LP7FE

功能描述:IC FRACT-N PLL W/SWEEPR 48LFCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:新产品 类型:* PLL:是 输入:时钟 输出:CML,LVDS,LVPECL 电路数:1 比率 - 输入:输出:1:14 差分 - 输入:输出:是/是 频率 - 最大值:3.2GHz 分频器/倍频器:是/无 电压 - 电源:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘,CSP 供应商器件封装:48-LFCSP(7x7) 标准包装:1

HMC7043LP7FETR

功能描述:IC FRACT-N PLL W/SWEEPR 48LFCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:在售 类型:时钟缓冲器 PLL:是 输入:时钟 输出:CMOS,LVDS,LVPECL 电路数:1 比率 - 输入:输出:1:14 差分 - 输入:输出:是/是 频率 - 最大值:3.2GHz 分频器/倍频器:是/无 电压 - 电源:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘,CSP 供应商器件封装:48-LFCSP(7x7) 标准包装:1

HMC7044LP10BETR

功能描述:IC JITTER ATTENUATOR 68LFCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:在售 类型:漂移衰减器 PLL:是 输入:CML,CMOS,LVDS,LVPECL 输出:CML,LVDS,LVPECL 电路数:1 比率 - 输入:输出:4:14 差分 - 输入:输出:是/是 频率 - 最大值:3.2GHz 分频器/倍频器:是/无 电压 - 电源:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:68-VFQFN 裸露焊盘,CSP 供应商器件封装:68-LFCSP-VQ(10x10) 标准包装:1

HMC704LP4E

功能描述:IC FRACT-N PLL 16BIT 24QFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR

HMC704LP4ETR

制造商:Hittite Microwave Corp 功能描述:IC FRACT-N PLL 16BIT 24QFN

HMC705LP4

制造商:HITTITE 制造商全称:Hittite Microwave Corporation 功能描述:6.5 GHz PROGRAMMABLE DIVIDER (N = 1 - 17)

HMC705LP4E

制造商:Hittite Microwave Corp 功能描述:IC DIVIDER HBT PROGR 24-QFN